- 您现在的位置:买卖IC网 > Sheet目录479 > MRF89XA-I/MQ (Microchip Technology)TXRX ISM SUB-GHZ ULP 32QFN

MRF89XA

2.14.5

FLOOR THRESHOLD CONTROL

REGISTER DETAILS

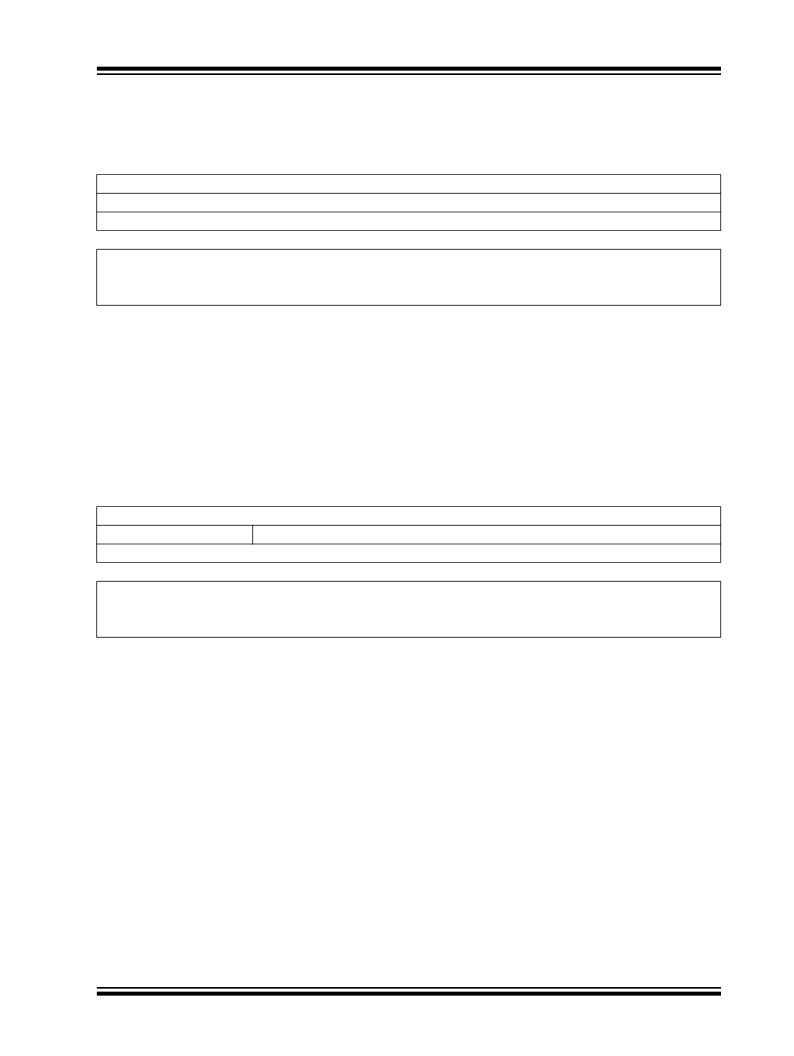

REGISTER 2-5:

FLTHREG: FLOOR THRESHOLD CONTROL REGISTER

(ADDRESS:0x04) (POR:0x0C)

R/W-0

R/W-0

R/W-0

R/W-0

R/W-1

R/W-1

R/W-0

R/W-0

FTOVAL<7:0>

bit 7

bit 0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

r = Reserved

bit 7-0

2.14.6

FTOVAL<7:0>: Floor Threshold OOK Value bits

The bits indicate Floor threshold in OOK receive mode.

FTOVAL<7:0> = 00001100 ≥ 6 dB (default)

FTOVAL assumes 0.5 dB RSSI Step

FIFO CONFIGURATION REGISTER

DETAILS

REGISTER 2-6:

FIFOCREG: FIFO CONFIGURATION REGISTER (ADDRESS:0x05) (POR:0x0F)

R/W-0

R/W-0

R/W-0

R/W-0

R/W-1

R/W-1

R/W-1

R/W-1

bit 7

FSIZE<1:0>

FTINT<5:0>

bit 0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

r = Reserved

bit 7-6

bit 5-0

FSIZE<1:0>: FIFO Size Selection bits

These bits set the size/number of FIFO locations.

11 = 64 bytes

10 = 48 bytes

01 = 32 bytes

00 = 16 bytes (default)

FTINT<5:0>: FIFO Threshold Interrupt bits

Setting these bits selects the FIFO threshold for interrupt source. Refer to Section 3.6.2, Interrupt

Sources and Flags for more information.

FTINT<5:0> = 001111 (default)

FIFO_THRESHOLD interrupt source’s behavior depends on the running mode (TX, RX or Stand-by

mode).

? 2010–2011 Microchip Technology Inc.

Preliminary

DS70622C-page 33

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MRF89XAM9A-I/RM

IC TXRX MOD 915MHZ ULP SUB-GHZ

MRX-001-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002SL-433DR-B

MODULE RCVR 433MHZ SAW LN 24DIP

MRX-005-915DR-B

MODULE RECEIVER 915MHZ 18DIP

MRX-005SL-915DR-B

MODULE RCVR 915MHZ SAW LN 24DIP

MRX-007-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-008-433DR-B

MODULE RECEIVER 433MHZ 18DIP

相关代理商/技术参数

MRF89XAM8A-I

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Ultra Low-Power, Integrated ISM Band Sub-GHz Transceiver

MRF89XAM8A-I/RM

功能描述:射频模块 868MHz Sub-GHz transceiver module

RoHS:否 制造商:Linx Technologies 产品:Transceiver Modules 频带:902 MHz to 928 MHz 输出功率:- 15.5 dBm to + 12.5 dBm 接口类型:UART 工作电源电压:- 0.3 VDC to + 5.5 VDC 传输供电电流:38.1 mA 接收供电电流:22.7 mA 天线连接器类型:U.FL 最大工作温度:+ 85 C 尺寸:1.15 mm x 0.63 mm x 0.131 mm

MRF89XAM8A-I/RM

制造商:Microchip Technology Inc 功能描述:, Leaded Process Compatible:Yes, Peak Re

MRF89XAM9A_12

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:915 MHz Ultra Low-Power Sub-GHz Transceiver Module

MRF89XAM9A-I/RM

功能描述:射频模块 915MHz Sub-GHz Transceiver Mod RoHS:否 制造商:Linx Technologies 产品:Transceiver Modules 频带:902 MHz to 928 MHz 输出功率:- 15.5 dBm to + 12.5 dBm 接口类型:UART 工作电源电压:- 0.3 VDC to + 5.5 VDC 传输供电电流:38.1 mA 接收供电电流:22.7 mA 天线连接器类型:U.FL 最大工作温度:+ 85 C 尺寸:1.15 mm x 0.63 mm x 0.131 mm

MRF89XAM9AT-I/RM

制造商:Microchip Technology Inc 功能描述:915 MHz Ultra Low-Power Sub-GHz Transceiver Module

MRF89XAT-I/MQ

功能描述:射频收发器 868/915/950 MHz Sub-GHz transceiver RoHS:否 制造商:Atmel 频率范围:2322 MHz to 2527 MHz 最大数据速率:2000 Kbps 调制格式:OQPSK 输出功率:4 dBm 类型: 工作电源电压:1.8 V to 3.6 V 最大工作温度:+ 85 C 接口类型:SPI 封装 / 箱体:QFN-32 封装:Tray

MRF8HP21080HR3

功能描述:射频MOSFET电源晶体管 HV8 2.1GHZ 160W NI780H-4 RoHS:否 制造商:Freescale Semiconductor 配置:Single 晶体管极性: 频率:1800 MHz to 2000 MHz 增益:27 dB 输出功率:100 W 汲极/源极击穿电压: 漏极连续电流: 闸/源击穿电压: 最大工作温度: 封装 / 箱体:NI-780-4 封装:Tray